Chapman & Hall/CRC Computational Science Series

# PROCESS ALGEBRA FOR PARALLEL AND DISTRIBUTED PROCESSING

MICHAEL ALEXANDER

WILLIAM GARDNER

# PROCESS ALGEBRA FOR PARALLEL AND DISTRIBUTED PROCESSING

### Chapman & Hall/CRC Computational Science Series

### SERIES EDITOR

### Horst Simon

Associate Laboratory Director, Computing Sciences

Lawrence Berkeley National Laboratory

Berkeley, California, U.S.A.

### AIMS AND SCOPE

This series aims to capture new developments and applications in the field of computational science through the publication of a broad range of textbooks, reference works, and handbooks. Books in this series will provide introductory as well as advanced material on mathematical, statistical, and computational methods and techniques, and will present researchers with the latest theories and experimentation. The scope of the series includes, but is not limited to, titles in the areas of scientific computing, parallel and distributed computing, high performance computing, grid computing, cluster computing, heterogeneous computing, quantum computing, and their applications in scientific disciplines such as astrophysics, aeronautics, biology, chemistry, climate modeling, combustion, cosmology, earthquake prediction, imaging, materials, neuroscience, oil exploration, and weather forecasting.

### **PUBLISHED TITLES**

PETASCALE COMPUTING: Algorithms and Applications Edited by David A. Bader

PROCESS ALGEBRA FOR PARALLEL AND DISTRIBUTED PROCESSING Edited by Michael Alexander and William Gardner

# PROCESS ALGEBRA FOR PARALLEL AND DISTRIBUTED PROCESSING

### EDITED BY MICHAEL ALEXANDER WILLIAM GARDNER

CRC Press is an imprint of the Taylor & Francis Group an **informa** business A CHAPMAN & HALL BOOK

Cover Image Credit: Intel Teraflops Research Chip Wafer from Intel, used with permission.

Chapman & Hall/CRC Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2009 by Taylor & Francis Group, LLC Chapman & Hall/CRC is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works Printed in the United States of America on acid-free paper 10 9 8 7 6 5 4 3 2 1

International Standard Book Number-13: 978-1-4200-6486-5 (Hardcover)

This book contains information obtained from authentic and highly regarded sources. Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright.com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

### Library of Congress Cataloging-in-Publication Data

Process algebra for parallel and distrubuted processing / editors, Michael Alexander and William Gardner.

p. cm. -- (Chapman & Hall/CRC computational science series) Includes bibliographical references and index.

ISBN 978-1-4200-6486-5 (alk. paper)

1. Parallel processing (Electronic computers) 2. Electronic data processing--Distributed processing. 3. Formal methods (Computer science) I. Alexander, Michael, 1970 Sept. 25- II. Gardner, William, 1952-

QA76.58.P7664 2009 004.01'51--dc22

2008029295

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

### **Contents**

| Fo | oreword                                                                                                                                                                | vii |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A  | cknowledgments                                                                                                                                                         | ix  |

| In | troduction                                                                                                                                                             | xi  |

| Ed | litors                                                                                                                                                                 | xix |

| Co | ontributors                                                                                                                                                            | xxi |

|    |                                                                                                                                                                        |     |

| Pa | art I Parallel Programming                                                                                                                                             | 1   |

| 1  | Synthesizing and Verifying Multicore Parallelism in Categories of Nested Code Graphs Christopher Kumar Anand and Wolfram Kahl                                          | 3   |

| 2  | Semi-Explicit Parallel Programming in a Purely<br>Functional Style: GpH<br>Hans-Wolfgang Loidl, Phil Trinder, Kevin Hammond,<br>Abdallah Al Zain, and Clem Baker-Finch | 47  |

| 3  | Refinement of Parallel Algorithms Fredrik Degerlund and Kaisa Sere                                                                                                     | 77  |

| Pa | art II Distributed Systems                                                                                                                                             | 97  |

| 4  | Analysis of Distributed Systems with mCRL2  Jan Friso Groote, Aad Mathijssen, Michel A. Reniers,  Yaroslav S. Usenko, and Muck van Weerdenburg                         | 99  |

| 5  | Business Process Specification and Analysis Uwe Nestmann and Frank Puhlmann                                                                                            | 129 |

| 6  | Behavioral Specification of Middleware Systems Nelson Souto Rosa                                                                                                       | 161 |

vi Contents

| 7   | Abstract Machine for Service-Oriented Mobility Hervé Paulino                                                                                                                   | 199 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8   | <b>Specifying and Implementing Secure Mobile Applications</b> <i>Andrew Phillips</i>                                                                                           |     |

| Pa  | art III Embedded Systems                                                                                                                                                       | 285 |

| 9   | Calculating Concurrency Using Circus Alistair A. McEwan                                                                                                                        | 287 |

| 10  | PARS: A Process Algebraic Approach to Resources and Schedulers<br>MohammadReza Mousavi, Michel A. Reniers, Twan Basten,<br>and Michel Chaudron                                 | 331 |

| 11  | Formal Approach to Derivation of Concurrent Implementations in Software Product Lines  Sergio Yovine, Ismail Assayad, Francois-Xavier Defaut, Marcelo Zanconi, and Ananda Basu | 359 |

| Inc | dex                                                                                                                                                                            | 403 |

### **Foreword**

This book brings together the state of the art in research on applications of process algebras to parallel and distributed processing.

Process algebras constitute a successful field of computer science. This field has existed for some 30 years and stands nowadays for an extensive body of theory of which much has been deeply absorbed by the researchers in computer science. Moreover, the theoretical achievements of the field are to a great extent justified by applications. The applications, in turn, strongly influence how the field evolves; some of the field's success may be attributed to frequently addressing needs that arose in practice.

Meanwhile, an explosion of complex systems of interacting components has been going on since the emergence of parallel and distributed processing. The complexity of the systems in question arises to a great extent from the many ways in which their components can interact. In developing a complex system of interacting components, it is important to be able to describe the behavior of the system in a precise way at various levels of detail, and to analyze it on the basis of the descriptions. Process algebras were and are developed for that purpose. Roughly speaking, a process algebra provides a collection of operators, a collection of equational laws for these operators, and a mathematical model of these laws. The latter allows for the behavior of a system to be described as composed of the emergent behaviors of several interacting components and for the described behavior to be analyzed by mere algebraic calculations.

The advent of process algebras was marked by the introduction of CCS in the seminal monograph *A Calculus of Communicating Systems* by Milner, published as volume 92 of Springer's Lecture Notes in Computer Science in 1980; the elaboration of CSP in the influential paper "*A theory of communicating sequential processes*" by Brookes, Hoare, and Roscoe, published in the *Journal of the ACM* in 1984; and the presentation of ACP as a strict algebraic theory in the paper "*Process algebra for synchronous communication*" by Bergstra and Klop, published in *Information and Control* in 1984.

The very first applications of process algebras were mostly concerned with the description and analysis of communication protocols. Later on, the applications became more and more advanced. Often, they were concerned with the description and analysis of embedded systems, and more recently with Internet-based distributed systems.

The applications of process algebras led to a number of developments. The very first applications brought about the development of basic algebraic verification techniques, i.e., basic techniques to establish—on the basis of algebraic

viii Foreword

calculations—whether the actual behavior of a system is in agreement with its expected behavior. The construction of basic tools to facilitate description and analysis followed. Later applications led to extensions of existing process algebras and the development of more advanced algebraic verification techniques. Both make it easier to describe and analyze the behaviors of the systems often encountered in practice nowadays: systems that may change their communication topology dynamically, systems that must react within a certain amount of time under certain circumstances, systems that exhibit at certain stages behavior that is stochastic in nature, systems that in their behavior depend on continuously changing variables other than time, etc. Experience with the existing process algebras led also to the development of special process algebras for the definition of the semantics of programming languages that support parallel programming or the design of microprocessors that utilize parallelism to speed up instruction processing.

It is difficult to foresee future developments and applications, yet some tendencies are noticeable. One area that is gaining momentum is specialized process algebras that are tailored to a certain paradigm for parallel or distributed computing or even to a certain technology for parallel or distributed computing. This fits in with the tendency to apply process algebras to describe and analyze a prototype of a certain class of systems. Such applications can be useful in understanding certain aspects of the systems of an emerging class. However, the adequacy of the prototypes may be a major issue, because often drastic simplifications are needed to keep the description manageable. There is also a tendency to apply process algebras outside the realm of computing, which shows promise.

Many theoretical developments in the field of process algebras were collected by Bergstra, Ponse, and Smolka in the *Handbook of Process Algebra*, published in 2001. In 2005, a workshop was organized in Bertinoro, Italy, to celebrate the first 25 years of research in the field. Several special issues of the *Journal of Logic and Algebraic Programming* are devoted to this workshop. Despite the importance of applications of process algebras for the success of the field, both the handbook and these special issues concentrate strongly on the theoretical achievements. This shortcoming is compensated for in a splendid way by this book, which brings together the state of the art in research on applications of process algebras.

**Kees Middelburg**

Programming Research Group University of Amsterdam, the Netherlands

### Acknowledgments

The editors are very grateful to those listed below who served as peer reviewers for contributions to this book. Their diligent and conscientious efforts not only helped us to make the final selection of chapters but also provided numerous valuable suggestions to the authors, resulting in a high-quality collection.

### Luca Aceto

School of Computer Science Reykjavik University Reykjavik, Iceland

### Lorenzo Bettini

Dipartimento di Informatica Universita' di Torino Torino, Italy

### Tommaso Bolognesi

CNR—Istituto di Scienza e Tecnologie dell'Informazione "A. Faedo" Pisa, Italy

### **Gerhard Chroust**

Systems Engineering and Automation Institute of Systems Sciences Johannes Kepler University of Linz Linz, Austria

### **Philippe Clauss**

Scientific Parallel Computing and Imaging Université Louis Pasteur Strasbourg, France

### Pedro R. D'Argenio

Department of Computer Science Facultad de Matemática, Astronomia y Fisica Universidad Nacional de Córdoba—CONICET Córdoba, Argentina

### John Derrick

Department of Computer Science University of Sheffield Sheffield, South Yorkshire, United Kingdom

### Gaétan Hains

Laboratoire d'Algorithmique, Complexité et Logique University of Paris-Est Créteil, France

and

SAP Labs France Mougins, France

### Michael G. Hinchey

Lero—The Irish Software Engineering Research Centre University of Limerick Limerick, Ireland

### Thomas John

Department of Information Systems Vienna University of Economics and Business Administration Vienna, Austria

### Kenneth B. Kent

Faculty of Computer Science University of New Brunswick Fredericton, New Brunswick, Canada

### Felix Mödritscher

Institute for Information Systems and New Media Vienna University of Economics and Business Administration Vienna, Austria

### **Raymond Nickson**

School of Mathematics, Statistics, and Computer Science Victoria University of Wellington Wellington, New Zealand

### Frederic Peschanski

Laboratoire d'Informatique de Paris 6 UPMC Paris Universitas Paris, France

### Luigi Romano

Department of Technology University of Naples Parthenope Naples, Italy

### Gwen Salaün

Department of Computer Science University of Málaga Málaga, Spain

### Emil Sekerinski

Department of Computing and Software McMaster University Hamilton, Ontario, Canada

### Kenneth J. Turner

Department of Computing Science and Mathematics University of Stirling Scotland, United Kingdom

### Huibiao Zhu

Software Engineering Institute East China Normal University Shanghai, China

### Introduction

Parallel processing is a rich and rapidly growing field of interest in computer science. Its spectrum ranges from small-scale, fine-grained multithreaded parallelism on single- and multicore processors to coarse-grained parallel execution on large, geographically dispersed distributed systems. With the rapid commoditization of multicore computers, developers are increasingly eager to exploit those multiple cores. Yet, this requires them to adopt parallel execution models that in turn need to explicitly address the underlying concurrency issues.

At the other end of the spectrum are applications that are spread out over a network of computers. They may be tightly coupled, such as for multiple computers cooperating on a single application in a high-performance cluster. Or, they may be loosely organized, as for mobile agents or service-oriented architectures (SOA). Regardless of the scale, a common requirement in parallel execution models is for carrying out interprocess communication and synchronization. Programmers know—or soon learn—that when this requirement is handled carelessly, a host of unpleasant failure modes tend to manifest: deadlocks, unrepeatable errors from race conditions, along with corruption of shared data.

One root cause is that the usual tools that programmers know best—mutexes, semaphores, condition variables, monitors, and message-passing protocols—are difficult to use correctly. Ad hoc design is common, and too often, success seems like a matter of good luck. In reality, many programmers new to parallel programming have an insufficient theoretical basis for what they are trying to do. Meanwhile, designers have learned that *modeling* is extremely helpful for all phases of system development—from understanding the requirements to expressing the specifications, and for systematically, even automatically, deriving an implementation "correct by construction" from the model. Yet, most popular modeling tools do not seem to give sufficient guidance for programming in concurrent environments.

Help is coming forth from computer scientists, who are fond of developing rigorous and logical ways of thinking and reasoning about computing. The purpose of this book is to show how one formal method of reasoning—that of *process algebra*—has become a powerful tool for solving design and implementation challenges of concurrent systems. Its power stems from providing a sound theoretical basis for concurrency, along with a formal notation that—in contrast to popular modeling techniques—is unambiguous. The price for obtaining the benefits is the necessity of coping with mathematical notation, symbols, and equations. Admittedly, this prospect may appear daunting to conventionally trained developers, who likely feel more comfortable drawing UML diagrams than puzzling out obscure equations. Fortunately, practitioners of process algebraic techniques are building domain-specific languages

xii Introduction

and application-specific tools that can be utilized by developers who then need to know less about the underlying theoretical elements. In such tools, the process algebra may be largely kept under the hood.

This book is not intended as a tutorial in process algebras, but there is space here for a brief orientation: Just as with the "algebra" we all learned in grade school, its ingredients include symbols standing for constant values and for variables, and operators that act on the symbols. While elementary algebra is concerned with manipulating numbers, a process algebra—or the synonymous term process calculus—is concerned with the creation, life, and death of processes that carry out computations. The emphasis is on interactions of processes among each other and with their environment. Symbols are used to stand for individual actions or events that a process may engage in; the processes themselves; channels, an abstraction used for interprocess communication; and data transmitted over the channels. Operators specify a sequential ordering of events; a choice between several events; if/then decisions; looping or recursive invocation of processes; composition of processes so that they execute concurrently, either synchronizing cooperatively on specified events, or running independently; and syntax for parameterizing and renaming so that process definitions can be reused in a modular fashion. Practitioners can use one of the classical process algebras mentioned in the Foreword—CCS, CSP, and ACP—or a more recent one such as the pi-calculus. Established process algebras have the advantage of the availability of automated tools that can be used for exploring a specification's state space and proving properties such as absence of deadlock (see Section 9.1 for a good explanation of these provable properties). Alternatively, practitioners can extend any of the base algebras by adding new symbols and operators, or even invent a new process algebra from scratch. A key advantage of formal, mathematical notations with rigorous semantics is that one can prove that particular conditions such as deadlock states do or do not exist, not just hope for the best, or discover them at runtime.

While the notion of process algebras goes back over two decades, what is new is the rapid proliferation of parallel computing environments that need their help in transforming sequential programming models to new ones better suited to parallelism. The urgent necessity for reliably exploiting concurrent computing resources has caused researchers to press classical process algebras into practical service, along with their invention of new ones. This book is intended as a showcase for recent applications of process algebras by current researchers from diverse parts of the international computer science community. While these contributions may appear largely theoretical due to the quantities of symbols and formulas, they are, in reality, process algebras applied to specific problems. The formalism is needed to establish the soundness of the theoretical basis, and to prove that the resulting tools are properly derived.

This book will be of special interest to students of process algebras, to practitioners who are applying process algebras, and to developers who are looking for fresh approaches to software engineering in the face of concurrency. The chapters are worth studying from two perspectives: first, those who identify with the problem Introduction xiii

domains (e.g., middleware systems or multicore programming) may ask, "Are the authors doing something that I could use, or can I adapt their approach?" and second, those who are interested in process algebras as a tool can ask, "How did the authors use a process algebra in their solution? What role did it play? How did they formally define it, and what did they prove in order to give it a sound basis?" A common pattern is to first create a process algebra whose symbols and operators are tailored to the problem domain (e.g., mobile agents). Next, a virtual (or abstract) machine (VM) is defined that executes specifications in the process algebra. Because both are formally defined, it is possible to prove that the VM is correct with respect to the algebra. The last step is to implement the VM, and this may be done by transferring it into a language that is semantically close, e.g., a functional programming language. Since the target language already possesses a compiler and/or runtime framework, the job of implementation is done, at least for prototyping and demonstration purposes.

The applied nature of the contributions is emphasized by organizing them into three target areas:

Part I Parallel Programming, Part II Distributed Systems, and Part III Embedded Systems.

We will now introduce each section and the chapters within it.

### Part I Parallel Programming

The specific problem in view here is how to parallelize an algorithm, so as to take advantage of, say, multiple processor cores. In an ideal world, parallelization would be accomplished automatically, perhaps by compilers that are able to detect implicit parallelism in source code and generate instructions for concurrent threads on their own. Bearing in mind that modern processors already do this, in effect, with instruction streams—selecting independent instructions for out-of-order execution by multiple logic units—it may seem surprising that compilers have largely failed to match this at the source code level. But processors are detecting and exploiting implicit fine-grained parallelism. In contrast, fine-grained parallelism in software algorithms is often not worth exploiting, since there are significant overheads in spawning, managing, and collecting results from concurrent threads, plus potential bottlenecks for access to shared data. Furthermore, automatically identifying higher-level, coarsegrained parallelism implicit in source code, while desirable from an efficiency perspective, has proven to be a very challenging problem.

Therefore, in the real world, parallelization is still done on a best effort basis by hand, and then it becomes a question of ensuring that a parallel version is truly equivalent to the serial version. Our contributors have developed formal methodologies for achieving precisely that result.

In Chapter 1, Anand and Kahl address programming the Cell BE (Broadband Engine) processor from Sony, Toshiba, and IBM. Its heterogeneous multicore architecture features eight Synergistic Processor Units (SPUs) with their own local storage on a token ring under the control of a general-purpose Power Processor Element (PPE) core. The SPUs are intended to act as coprocessors for the PowerPC, being loaded on-the-fly with instructions and data, and coordinating via signals. The authors'

xiv Introduction

Coconut tool set provides the means to take an algorithm written in a domain-specific language (DSL) embedded in Haskell, and parallelize it for the Cell BE. The key to their approach is utilizing a graph-based internal representation of the program's data and control flows, which are then targeted to a VM that deals strictly with concurrency issues, e.g., data transfers and interprocessor signaling. The programmer manipulates the graph to create a high-performance schedule on the eight SPUs, with the authors' tool being used to verify that the scheduled version is correct, i.e., independent of a parallel execution order. The role of process algebra in this approach is to define the VM language, and then carry out correctness verification. While currently targeted to the Cell BE, their approach can potentially be ported to other multicore platforms.

In Chapter 2, Loidl et al. take an approach similar to that in Chapter 1 in that they also develop a runtime environment, Glasgow parallel Haskell (GpH), that can be ported to different parallel platforms, and they also focus on a functional programming language. Rather than attempting to automatically extract parallelism from GpH source code, they allow programmers to insert "par" and "seq" constructs into a program to give "semi-explicit" direction while carrying out successive steps of refinement to a parallel version. Their runtime environment, GUM, has been ported to a number of different parallel platforms.

These two chapters describe tools that are currently being used to program parallel systems. In comparison, Chapter 3 is more theoretical. Degerlund and Sere present an approach to taking algorithms described using another formal model called *action systems*, and developing an equivalent parallel version useful for scientific computing. An action system is specified using a process algebra called *refinement calculus*. The steps of refinement are used to introduce parallelism into the action system, with execution on a parallel target platform in view. The formal semantics of the refinement calculus ensure that the transformations are correct.

### Part II Distributed Systems

Process algebras find their natural application in terms of formally modeling and verifying the behavior of distributed systems. Distributed systems are quite diverse, and this section also has the largest number of chapters.

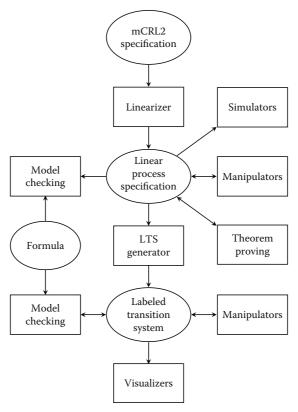

We start with the work of Groote et al. in Chapter 4, who have developed a process algebra, mCRL2, which is specifically targeted at distributed applications. Its provision for local communication scope (i.e., restricted to a hierarchy of processes), as opposed to purely global scope, makes it useful for describing component-based architectures. mCRL2 also accommodates true concurrency "multiactions" distinct from interprocess communication, and supports the specification of abstract data types and action times. The authors have built tools capable of analyzing properties and simulating applications specified using mCRL2. This chapter has examples of visualizing the state space of a specification by means of a generated graphic.

One category of distributed systems that is currently gaining attention is the SOA that enables a business process to be automated by invoking software components located across a network. However, business processes and services described in words are subject to misinterpretations, leading to errors in integrating SOAs. A key

*Introduction* xv

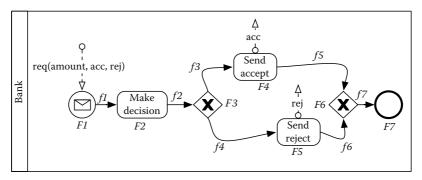

area for formalization is turning prose descriptions into unambiguous specifications. Chapters 5 and 6 make contributions in this area.

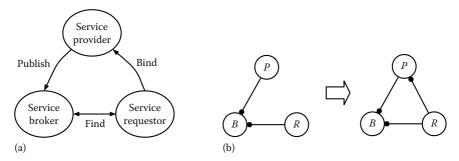

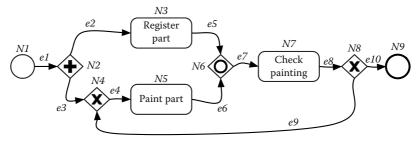

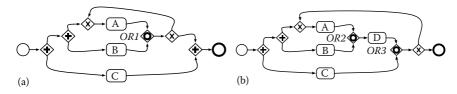

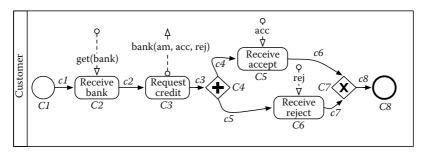

Chapter 5 shows Nestmann and Puhlmann using an existing process algebra, the pi-calculus, to formally specify business processes. Their approach allows business processes to be captured in the form of Business Process Modeling Notation (BPMN) process graphs—whose nodes specify interactions such as parallel split, synchronizing merge, exclusive choice, and others—and then converted to pi-calculus agents enhanced by the authors' "trio" construct. Interactions of business processes and services can be formally modeled, and the models analyzed for various soundness properties. The authors have created a tool to automate the property analysis.

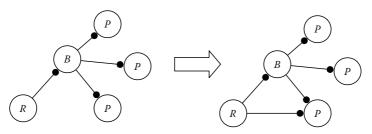

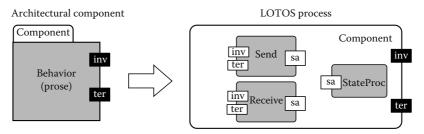

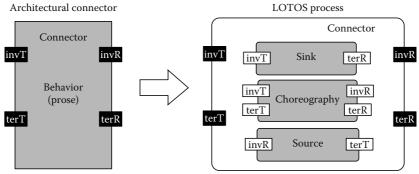

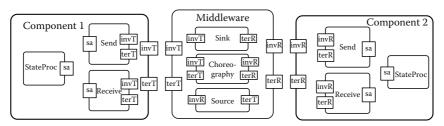

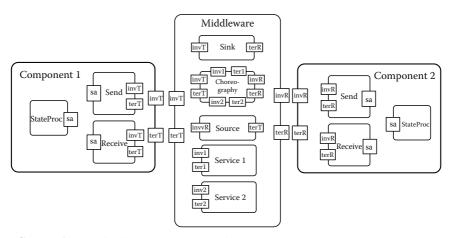

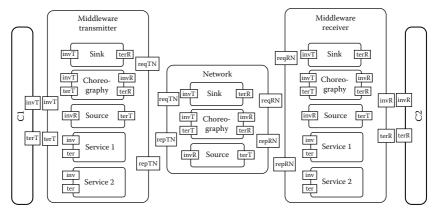

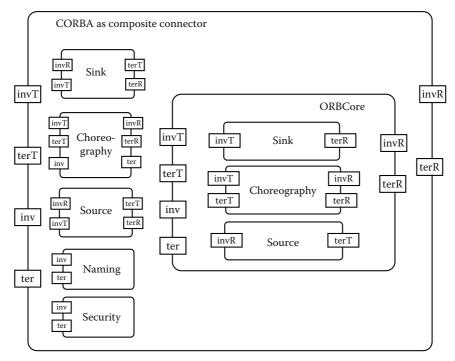

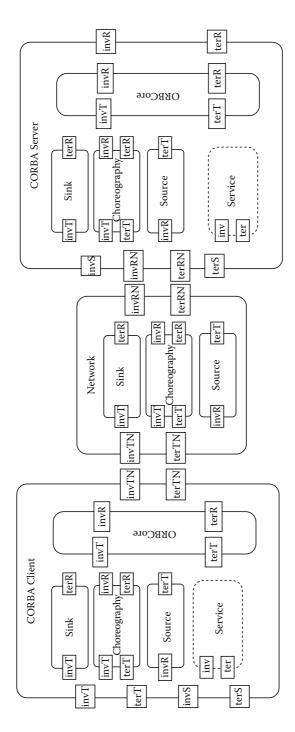

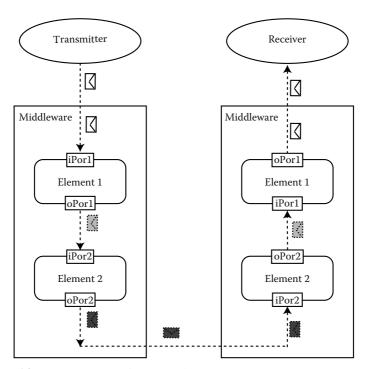

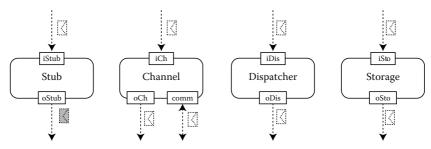

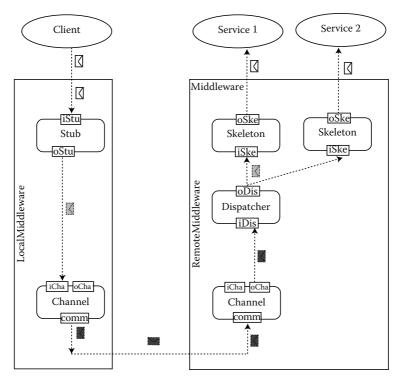

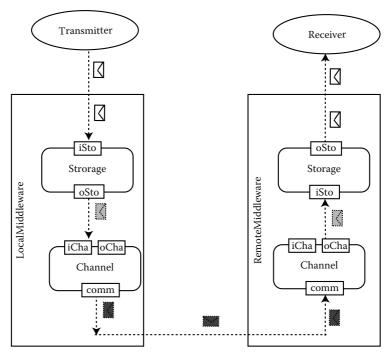

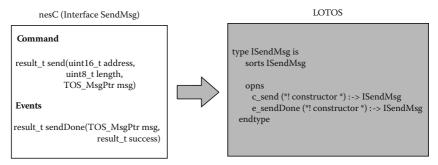

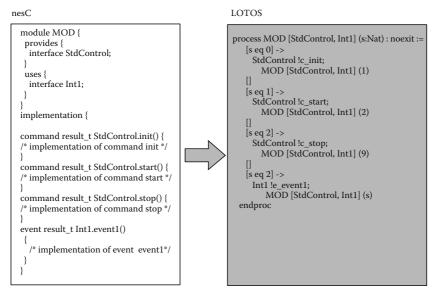

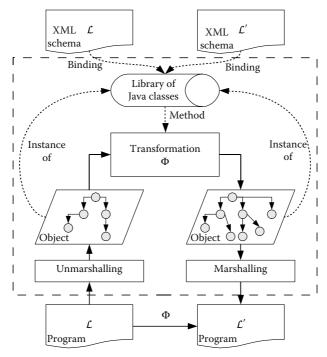

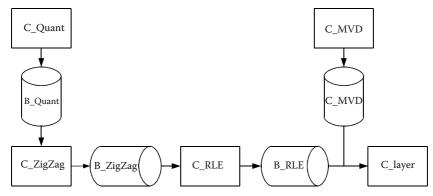

In Chapter 6, Rosa uses an ISO-standard process algebra, LOTOS, to formalize the construction of middleware systems. Each architectural component is specified as a single LOTOS process, which defines the component's structure—the ports available to connect to other components—and behavior in process-algebraic terms. The use of a formal notation as an architecture description language, in contrast to ambiguous prose descriptions, aids both would-be service providers and service integrators, and makes it possible to prove temporal properties of an architecture. The author further employs this technique to create a library of abstract message-oriented components for use in defining middleware. A third demonstration formalizes middleware for wireless sensor networks.

Another manifestation of distributed systems is based on the notion of mobile agents moving around a network. The purpose is to send software to the data rather than pulling the data down to a computation node. As argued in Chapter 8, mobility helps to minimize the impact of two problems common to distributed systems: network latency and network failure. Systems based on mobile agents will also benefit from formal descriptions, especially when it comes to ensuring security. Chapters 7 and 8 deal with mobility. As in Chapters 1 and 2, the authors of Chapters 7 and 8 take the approach of formally defining a VM.

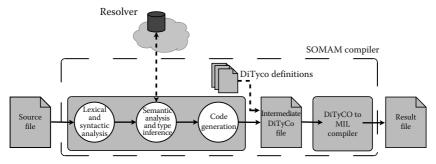

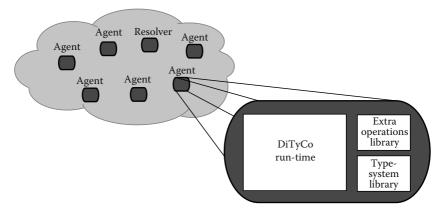

In Chapter 7, similar to Chapters 5 and 6, Paulino targets SOA and middleware. His VM, service-oriented mobility abstract machine, is based on an extension of the pi-calculus. By programming for the VM, programmers can be abstracted from the details of the network while still utilizing mobility. The author's strategy for deployment is to execute the machine on network nodes running an existing framework called DiTyCO.

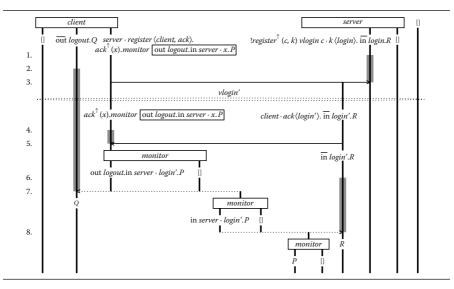

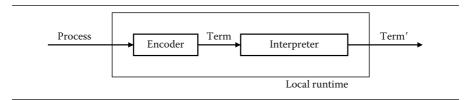

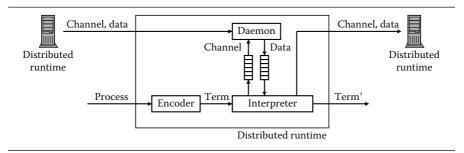

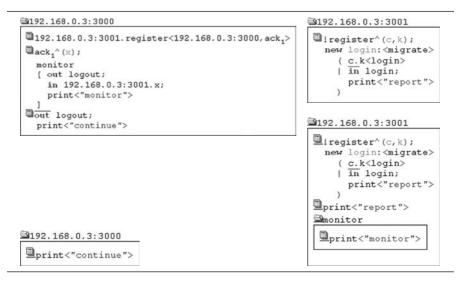

In Chapter 8, Phillips presents his Channel Ambient (CA) calculus for specifying mobile applications. The textual notation also has a helpful graphical counterpart. Based on the abstract notion of an "ambient"—which may stand for a machine, a mobile agent, or a software module—the CA calculus provides operations whereby ambients may interact, and migrate in and out of each other, via channels. Security properties can be verified for a given specification. The execution target is called the Channel Ambient Machine (CAM), and its correctness with respect to the CA calculus is proven by the author. His implementation strategy is to map the CAM to a functional programming language, OCaml, that can then be executed on network nodes.

xvi Introduction

### Part III Embedded Systems

While an exact definition of an embedded system is debatable, it is generally described as a product that contains within it some combination of software running on a general- or special-purpose processor, plus associated custom digital logic. The latter is commonly used to accelerate specific portions of calculations, which would otherwise require a more expensive processor in order to meet timing constraints. The term "embedded" refers to the fact that the end user is not necessarily aware that the product contains a computer, and, in any case, cannot utilize the computer for some other purpose. Embedded systems have special design constraints because, unlike software for desktop or server computers, the products have a significant recurring cost, such as parts, assembly, packaging, labor, etc., in addition to the nonrecurring engineering cost that goes into developing and interfacing the software and hardware components. Furthermore, they may have to meet rigorous requirements of power consumption (battery life), size, and weight. Cell phones and digital cameras are common examples. Robotic devices, such as autonomous vacuum cleaners, are embedded systems. Some are safety-critical, such as an antilock brake controller. The aim of choosing the best combination of hardware and software is to meet all the performance requirements at the lowest manufacturing cost, i.e., offering a sufficient set of features at a competitive price.

Parallelism in embedded systems comes in several forms: embedded devices are often designed in terms of concurrent threads, some monitoring sensor inputs, others computing outputs, or actuating control outputs. Some have multiple processors, which may be heterogeneous, such as a 16-bit microcontroller plus a DSP, and some have hardware/software concurrency. They are often designed and marketed in a family of related products with more/fewer features, or adding features over time, or that utilize differing HW technology more favorable to different production quantities. Formal methods are very attractive for ensuring reliability, especially for safety-critical products, and those in hard-to-access locations.

In Chapter 9, McEwan leads off with a contribution targeted at formally deriving a hardware implementation, although his technique is also applicable to software. As with Chapter 3, which combines the state-based formalism of action systems with the event-based refinement calculus, McEwan combines state-based Z with the event-based process algebra CSP, in a formal methodology called Circus. Z is used to provide a formal model for the data. Refinement toward an implementation proceeds by applying laws that safely inject parallelism into a sequential specification. The target language, Handel-C, used to synthesize digital logic, is close to CSP. Circus is flexible enough to allow engineering choices to guide the refinement, while still ensuring that the resulting implementation is correct.

Typical parallel systems leave the scheduling of multiple processes to the operating system under the assumption of adequate CPU time and memory. Accordingly, many process algebras used to specify parallel systems do not have visibility into process scheduling, yet real-time embedded systems must guarantee responses within certain time constraints, and do so in the context of limited resources (chiefly CPU time and memory). Formal notations to specify resource requirements such as timing constraints are therefore of great utility in the embedded domain.

*Introduction* xvii

In Chapter 10, Mousavi et al. address this problem by developing a pair of process algebras, together called PARS: one to specify processes, and another to specify scheduler behavior. The two, combined, produce a scheduled system.

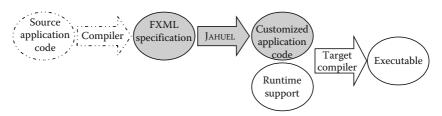

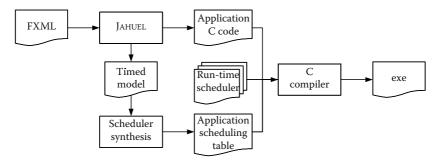

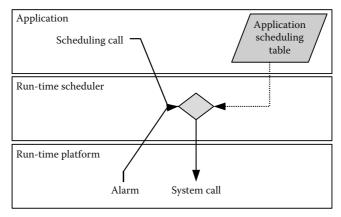

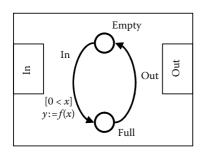

The final chapter, Chapter 11, considers embedded systems through the lens of product lines, in which reuse of concurrent artifacts across different hardware platforms is emphasized. Yovine's solution is to use an algebraic language, FXML, to specify concurrent behavior, associated control and data dependencies, and timing constraints. FXML specifications are then processed by a software synthesis tool, Jahuel, to yield an implementation customized for a given platform. Platforms may differ in the means by which concurrency is supported and interprocess synchronization and communication are carried out. FXML can also be used in a design automation toolset as an intermediate specification with formal semantics. Moreover, one can define a translation of a nonformal language into FXML, thus giving the language a formal semantics and opening up the possibility of verification.

We would be remiss not to acknowledge a "dark cloud" in the picture: the challenge of scaling up some of these techniques for industrial-sized applications. Such specifications may have so many states that automated verification tools cannot reach them all in reasonable time. This drawback may not be evident from these chapters themselves, since the authors were forced to use small examples, both for the sake of clarity and due to space limitations. Yet some claim to have applied their techniques to larger-scale problems. For more details, consult the references to the authors' own related work, and they will be pleased to answer queries.

The process of collecting these chapters has highlighted for us, as educators, that colleges and universities have further to go in training undergraduates to be comfortable with concurrency and skilled in reliable methods of parallel programming. More exposure to formal methods is also needed, so that these approaches do not appear so foreign. As it is, in most software development curriculums, particularly in North America, formal methods are more "honored in the breach" than by systematic instruction. At the same time, researchers will do well to embed their process algebraic techniques into tools suitable for users without special training, in order to widen their prospects for adoption.

To conclude, we offer this book as an early collection of research fruits in what will undoubtedly become a burgeoning growth industry in the coming years, and to which the editors are eager to contribute their own research.

### **Editors**

Michael Alexander holds degrees in electrical engineering (Technologisches Gewerbemuseum [TGM]), business administration (University of Southern California), and economics (University of Vienna). He is a supervisor in the Vienna, Austria KPMG IT Advisory practice. His experience includes teaching and research at Wirtschaftsuniversität Wien; as a lecturer and product management at IBM, Siemens, Nortel Networks, and Alcatel; as a product line manager for ADSL and Optical Access Networks. He has authored a textbook on networks and network security [1] published by Hüthig/Verlagsgruppe Süddeutsche, and has edited a special issue on mathematical methods in network management of the Wiley International Journal of Network Management. For the last four years, Dr. Alexander has served as the program committee chair for the Workshop on Virtualization in High-Performance Cluster and Grid Computing (VHPC). His current research interests include computer networking, formal methods, network management, concurrency, payment systems, machine learning methods in operations research, and e-learning.

William Gardner received his bachelor's degree in computer science from the Massachusetts Institute of Technology. Subsequently, he pursued his career in software engineering at Litton Systems (Canada) Ltd., Toronto, working primarily on embedded systems for defense customers. Returning to graduate school later in life, he did his doctoral research in the VLSI Design and Test Group in the Department of Computer Science at the University of Victoria, British Columbia, Canada. His interests are chiefly in design automation starting from formal specifications, particularly targeting embedded systems via hardware/software codesign. His software synthesis tool CSP++ [2] translates formal CSP specifications into executable C++. Its design flow features "selective formalism," where a system's control backbone is specified and verified in CSP, and then the principal functionality is provided by plugging C++ user-coded functions into the backbone, to be actuated by CSP events and channel communications. He was formerly on the faculty of Trinity Western University, British Columbia, Canada, and moved in 2002 to the University of Guelph, Ontario, Canada, where he is currently an associate professor in the Department of Computing and Information Science. With his graduate students, he has been participating in the R2D2C project at the NASA Goddard Space Flight Center, which involves automatic code generation from scenarios via under-the-hood formal specifications [3]. Dr. Gardner teaches courses on software development, operating systems, embedded systems, and hardware/software codesign.

xx Editors

### References

- [1] M. Alexander, *Netzwerke und Netzwerksicherheit—Das Lehrbuch*, Hüthig Telekommunikation, Heidelberg, 2006.

- [2] W.B. Gardner, Converging CSP specifications and C++ programming via selective formalism, *ACM Transactions on Embedded Computing Systems* (TECS), Special Issue on Models and Methodologies for Co-Design of Embedded Systems, 4(2), 302–330, May 2005.

- [3] J. Carter and W.B. Gardner, Converting scenarios to CSP traces with Mise en Scene for requirements-based programming, *Innovations in Systems and Software Engineering*, 4(1), April 2008.

### **Contributors**

### Abdallah Al Zain

School of Mathematical and Computer Sciences Heriot-Watt University Edinburgh, United Kingdom

### **Christopher Kumar Anand**

Department of Computing and Software McMaster University Hamilton, Ontario, Canada

### Ismail Assayad

VERIMAG Grenoble, France

### Clem Baker-Finch

Department of Computer Science Australian National University Canberra, Australia

### **Twan Basten**

Department of Electrical Engineering Eindhoven University of Technology Eindhoven, the Netherlands

### Ananda Basu

VERIMAG Grenoble, France

### Michel Chaudron

Leiden Institute of Advanced Computer Science Leiden University Eindhoven, the Netherlands

### Francois-Xavier Defaut

VERIMAG Grenoble, France

### Fredrik Degerlund

Turku Centre for Computer Science Åbo Akademi University Turku, Finland

and

Department of Information Technologies Åbo Akademi University Turku, Finland

### Jan Friso Groote

Department of Mathematics and Computer Science Eindhoven University of Technology Eindhoven, the Netherlands

### **Kevin Hammond**

School of Computer Science University of St Andrews St Andrews, Scotland United Kingdom

### **Wolfram Kahl**

Department of Computing and Software McMaster University Hamilton, Ontario, Canada

### Hans-Wolfgang Loidl

Institut für Informatic Ludwig-Maximilians-Universität Munich, Germany xxii Contributors

### Aad Mathijssen

Department of Mathematics and Computer Science Eindhoven University of Technology Eindhoven, the Netherlands

### Alistair A. McEwan

Department of Engineering University of Leicester Leicester, United Kingdom

### MohammadReza Mousavi

Department of Mathematics and Computer Science Eindhoven University of Technology Eindhoven, the Netherlands

### **Uwe Nestmann**

School of Electrical Engineering and Computer Science Berlin Institute of Technology Berlin, Germany

### Hervé Paulino

Computer Science Department New University of Lisbon Lisbon, Portugal

### **Andrew Phillips**

Microsoft Research Cambridge, United Kingdom

### Frank Puhlmann

Hasso-Plattner-Institut Potsdam, Germany

### Michel A. Reniers

Department of Mathematics and Computer Science Eindhoven University of Technology Eindhoven, the Netherlands

### **Nelson Souto Rosa**

Centre of Informatics Federal University of Pernambuco Recife, Brazil

### Kaisa Sere

Department of Information Technologies Åbo Akademi University Turku, Finland

### **Phil Trinder**

School of Mathematical and Computer Sciences Heriot-Watt University Edinburgh, Scotland, United Kingdom

### Yaroslav S. Usenko

Department of Mathematics and Computer Science Eindhoven University of Technology Eindhoven, the Netherlands

### Muck van Weerdenburg

Department of Mathematics and Computer Science Eindhoven University of Technology Eindhoven, the Netherlands

### Sergio Yovine

VERIMAG Grenoble, France

### Marcelo Zanconi

VERIMAG Grenoble, France

## Part I Parallel Programming

### Chapter 1

### Synthesizing and Verifying Multicore Parallelism in Categories of Nested Code Graphs

### **Christopher Kumar Anand and Wolfram Kahl**

### **Contents**

| 1.1  | Introdu            | action                                               | 4  |  |

|------|--------------------|------------------------------------------------------|----|--|

|      | 1.1.1              | Related Work                                         | 5  |  |

|      | 1.1.2              | Cell BE Architecture and the Virtual Machine         | 6  |  |

|      | 1.1.3              | Background on Coconut                                | 7  |  |

|      | 1.1.4              | Overview                                             |    |  |

| 1.2  | Nested Code Graphs |                                                      |    |  |

|      | 1.2.1              | Data-Flow Graphs and Parallelism                     |    |  |

|      | 1.2.2              | Nonconcurrent Control-Flow Graphs                    |    |  |

|      | 1.2.3              | Control-Flow Graphs and Concurrency                  |    |  |

|      | 1.2.4              | Concurrent Interpretation of Data-Flow Graphs        |    |  |

| 1.3  | Efficie            | nt Multicore Parallelism                             | 15 |  |

| 1.4  | Motiva             | ation for Multicore Virtual-Machine Model            | 17 |  |

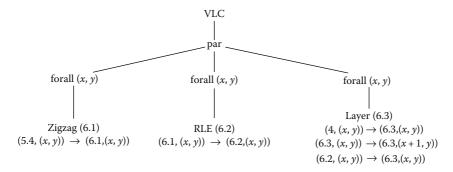

| 1.5  | Virtual            | -Machine Language                                    | 18 |  |

|      | 1.5.1              | Virtual-Machine Instruction List                     |    |  |

| 1.6  | Schedu             | ıling Algorithm                                      | 24 |  |

|      | 1.6.1              | Payload Scheduling                                   |    |  |

|      | 1.6.2              | Payload Buffer Allocation + Communication Generation |    |  |

|      | 1.6.3              | Communication Scheduling                             | 27 |  |

| 1.7  | Concu              | rrency Verification                                  | 28 |  |

|      | 1.7.1              | Motivating Example                                   | 30 |  |

|      | 1.7.2              | Strictly Forward Inspection of Partial Order         |    |  |

|      | 1.7.3              | State                                                |    |  |

|      | 1.7.4              | Proof of Theorem                                     |    |  |

| 1.8  | Conclu             | ısion                                                |    |  |

| Ackn |                    | nents                                                |    |  |

|      | ences              |                                                      | 42 |  |

### 1.1 Introduction

Current trends in high-performance processor technology imply that the programming interface is becoming more complicated. The pronounced shift toward pervasive Single Instruction Multiple Data (SIMD) parallelism, and the introduction of heterogeneous computing elements, including hierarchically distributed memory (encompassing conventional distributed memory, streaming memory, software-directed caches, and private memories), will require changes in software development tools.

Among the first generation of such processors, the Cell Broadband Engine (BE) is the most widely deployed. Using its resources efficiently requires explicit synchronisation of both code and data, and packaging of both to fit in small memory spaces and constrained communication infrastructures.

The COde CONstructing User Tool (Coconut) project has the aim of capturing the entire design and development process for safety-critical, high-performance scientific software, e.g., medical imaging, in a sequence of formal specifications. The hardware-specific parts of Coconut currently target a single Cell BE. See Section 1.1, for background on the Cell BE and Coconut.

This chapter describes the support Coconut provides for multicore parallelism, including the way that concurrent control flow is represented in nested hypergraphs, the way multicore issues are abstracted into a virtual machine, and the support Coconut provides for developers of parallelization patterns. This support includes a linear-time algorithm to verify the soundness of a parallelization. For the developer, verification eliminates the need for time-consuming parallel debugging, and the analogy between the virtual machine and a superscalar CPU provides a familiar way of thinking about scheduling.

The key to being able to provide an efficient verification tool is the abstraction provided by modeling multicore communication as a simple process algebra. Simplicity is justified because parallelism is not an inherent part of algorithm specifications in the domain of scientific computation, it is only added to implementations to meet performance targets, so the process algebra only needs to model the patterns of communication which support this. Adding additional features to support general control flow would significantly complicate verification, and could be used by developers to implement program logic, making programs much harder to understand, and thereby reducing programmer productivity.

The Coconut tool set uses as intermediate representations of programs and program fragments, a variant of term hypergraphs we call "code graphs." Term graphs have a long history as an efficient implementation of symbolic expressions. A certain kind of term graph also provides a natural model of a resource-conscious kind of categories (gs-monoidal categories, [8]); this provides a useful justification of many kinds of algebraic data-flow graph transformations. To combine control flow and data flow, we nest the simple data-flow code graphs inside an outer-level code graph with control-flow semantics, similar to the two different semantics of flownomials [19]. Software pipelining, i.e., instruction reordering to make better use of instruction pipelines and multiple-issue queues, is an algebraic transformation involving both levels of such nested code graphs.

This approach naturally extends to modeling (restricted) concurrency: We introduce a third, outer layer for explicit concurrency, with a semantics more on the dataflow side (this is related with the implicit concurrency in pure functional programs), but again with some control-flow characteristics.

Algebraic transformations crossing the outer two levels in such three-level nested hypergraphs are used to map potential concurrency to explicit concurrency, and to hardware parallelism. On the level of multicore processors, this will involve the automatic introduction of appropriate synchronization instructions or, in the opposite direction, the elimination of such concurrency primitives for the purpose of verifying against a concurrency-independent specification.

This chapter presents the control flow at the middle multicore level. In conventional programs, this level of control flow is usually encoded in library calls (e.g., MPI [33,38]) in the program text. Our approach is to make this disjoint in a separate level of the graph. This allows for a simple verification of correctness for deeply pipelined data-flow graphs through a network of cores (processors). As a result, whether multicore parallelism is directed by user code, user-code generators, or automatic parallelization, the programmer/compiler writer can focus on tuning for performance, and check correctness in a computation which grows linearly with program size, and quadratically in the complexity of the hardware.

The distinguishing feature of code graphs at this level is that they are presented as ordered lists of instructions. Proofs of sound parallelization work by going through the list in order, maintaining a limited set of state information (status of signaling and data transfers, contents of buffers). Any ambiguity (from a race condition) or deadlock can be flagged in the presented program.

### 1.1.1 Related Work

This work is the first step in bringing together disconnected research efforts in (1) verification of concurrent programs, (2) scheduling for distributed processors, and (3) decomposition of large numerical problems.

Practical parallel computation is a special subset of the set of concurrent programs. We have defined a precise subset of the vaguely defined set "parallel computation." Verification of correctness in this subset should be simpler than in the larger set, but many important ideas come from efforts to verify general concurrent programs. We make fundamental use of partial orders in analyzing concurrency within our programs. Godefroid and several collaborators have demonstrated that partial order methods can be much more efficient than other methods for general concurrent problems [16,20]. In the language of Ref. [16], we construct a partial order in such a way as to show that there are no backtracking points, i.e., no points where a different execution sequence would have led to a different result. Our implementation is much simpler, with tight complexity and memory bounds, because it is tailored to the restricted set of programs we consider. The trade-off is that the programs we are able to consider are orders of magnitude larger than typical concurrency benchmarks.

We target the Cell BE processor, using matrix multiplication as our first benchmark, as do [5]. Our approach differs in that we present the programmer with an

unconventional interface via domain-specific languages (DSLs) embedded in Haskell. DSLs [14] can be a useful tool for making special-purpose software development accessible to domain experts; Ref. [13] and, in particular, Hudak [25,26] showed that embedding DSLs in Haskell has significant advantages both for implementability and for usability.

There is a lot of literature related to loop decomposition, and specifically the decomposition of large operations in linear algebra. The generation of consumers used in our scheduling algorithm implicitly encodes a loop tiling (see Refs. [21,22]). Research in this direction is currently considering much more complex computational examples than we are able to at this time, and will provide a rich set of benchmarks for the future. That said, some of the work on tiling will have to be reconsidered in light of the shift from computational to main-memory bottlenecks. We hope that our tool will accelerate the development of patterns of communication involving many point-to-point pipelined transfers.

### 1.1.2 Cell BE Architecture and the Virtual Machine

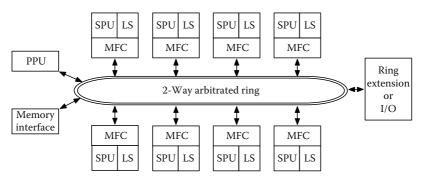

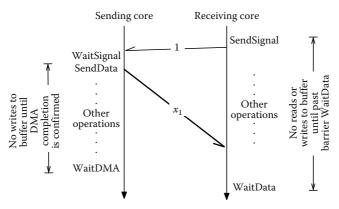

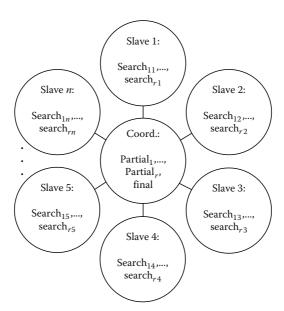

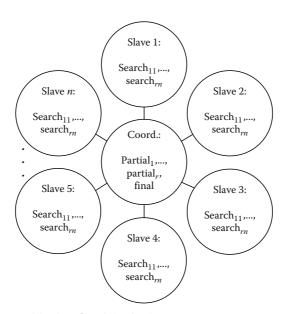

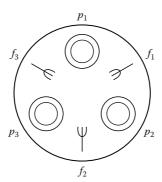

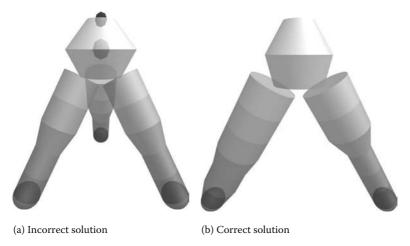

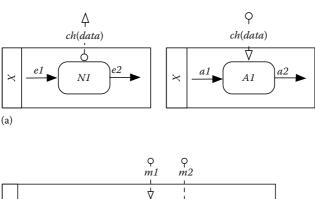

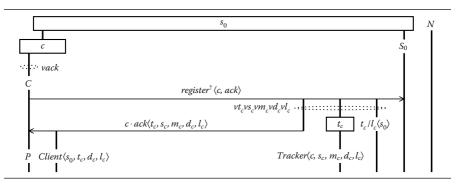

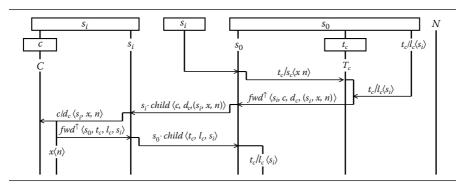

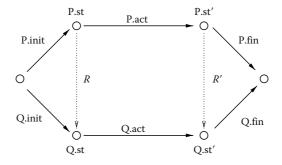

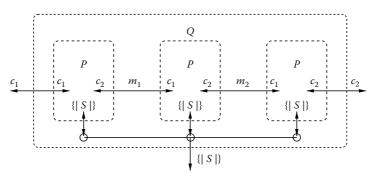

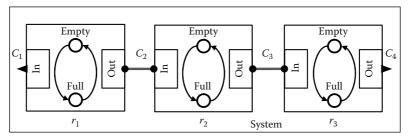

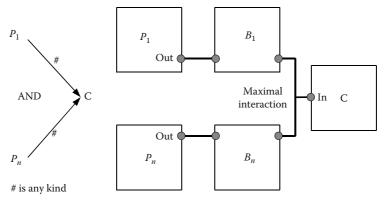

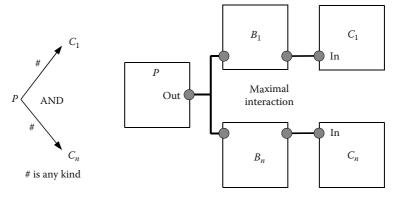

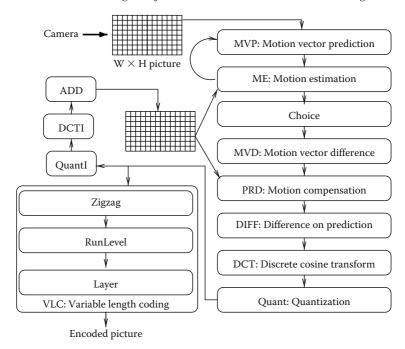

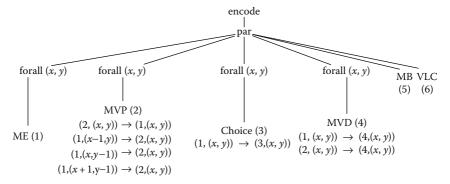

The Cell BE architecture exposes both computational and data-flow resources to user-level programming. In Figure 1.1, one sees the main computational resources. The synergistic processing units (SPUs) do not have direct access to the multilayer token ring, but must go through the attached memory flow controller (MFC), which operates most efficiently when executing reorderable lists of direct memory access (DMA) instructions. The PowerPC Unit (PPU) is capable of general computation, but has much lower performance than the SPUs. The initial implementations of the Cell BE include interfaces to extend the ring architecture to multichip rings or switched networks [7].

In implementing the approach to concurrent control flow presented in this chapter, the PowerPC (PPC) core manages run-time start up (address resolution, code loading, etc.).

Our virtual machine model was designed with the Cell BE in mind, but could easily be adapted to other architectures. If an architecture does not support signals,

**FIGURE 1.1:** Bus diagram for Cell BE.

they could be emulated using data transfers. Just as object code optimized for one generation of a processor family may run poorly on the next generation, the performance of a generated program will depend on it being optimized for the right implementation of the virtual machine. If signals are not supported, some patterns of communication may become more expensive relative to other patterns.

The current Cell BE is a tightly coupled single-chip device. For this reason, fault tolerance is not designed into the virtual machine, and efficiently handling partial equipment failure would require extensions to the virtual machine model.

### 1.1.3 Background on Coconut

Coconut is architected with both long- and short-term correctness requirements. In the long-term, we believe that safety-critical applications like medical imaging should come with meaningful correctness guarantees. Meaningful, to the patient, means that the image which comes out is proven to be the result of applying algorithms with known specifications and understandable physical inputs. Algorithms can be incorrect, but they should be specified by experts in the field. No low-level optimizations should be taken without floating up their consequences to the algorithm level for approval. Specifications at this level must include concrete anchors in the physical universe, including not just units, but oriented coordinate systems, etc. High level User Specification of Constraints (HUSC) [40] is a prototype including special implementations of type inferencing and alternatives suited to these applications.

Current practice starts with an informal specification of the algorithm, possibly supplemented with a partial implementation in a mathematical scripting language. This specification is translated into different types of low-level specifications and finally implemented in an imperative language, possibly including assembly language.

The Coconut workflow involves no unverifiable human translation of specifications or manual editing of assembly code. Code optimization experts contribute by formally specifying patterns of efficient implementation as code transformations or code generators. At this time, all transformations and leaf functions are specified in Haskell. For the lowest-level patterns, which are implemented without control flow (although they may contain control flow synthesized using logical and permutation instructions) we have defined a DSL embedded in Haskell, including a number of support tools such as simulation and symbolic execution. Such tools are important not just for verifying of correctness, but for pinpointing errors in code under development.

Much of the technical difficulty in optimizing code (whether by human or by compiler) is the recognition of patterns of control flow expressed using conventional patterns. The Coconut strategy for avoiding this is to provide more expressive control constructions at the language level. One of these is the MultiLoop [3]. Novel control structures require novel instruction scheduling. Explicitly Staged Software Pipelining [39] is a novel approach to scheduling loops which supports the MultiLoop.

This work defines a language for concurrent control flow, and the principal tool for both debugging patterns and verifying correctness.

Coconut is being implemented from the bottom up to insure that intermediate representations do not interfere with the identification of optimizable patterns of execution. One advantage of this approach is that we are able to produce high-performance C-callable single-core functions, and using the infrastructure defined here, we will be able to provide libraries which encapsulate optimal parallel execution. At this point, Coconut will be able to generate the most difficult aspects to verify in our target applications. For many applications, verification of this level of computation is enough. There is no plan to allow Coconut-generated code to call functions written in other languages, since this would make verification much more difficult.

This strategy allows us to earn early dividends from the considerable investment required to build verifiably correct software at this level of performance.

Coconut is implemented in Haskell, except for type inferencing in HUSC. Haskell is used for developer-productivity reasons, mostly strong and flexible typing. The current DSL embedding takes advantage of Haskell language features, and the existence of support for literate code, and these features are appreciated by novice users, but another pure functional language could have been used.

### 1.1.4 Overview

We explain in Section 1.2 how directed hypergraph syntax naturally integrates data flow and concurrent control flow, and summarize how we use these code graphs in nested arrangements for different aspects of the generation of high-performance code.

We then turn our attention to implementation aspects of multicore parallelism (Section 1.3), contrasting it with other kinds of parallelism, to provide the background for the decision (Section 1.4) to define a virtual machine for encapsulating certain low-level aspects of targeting multicore architectures. The details of this virtual machine are then presented in Section 1.5, and in Section 1.6 we show how we produce, partially guided by graph transformations, a multicore program scheduled to hide communication latencies as far as possible. To independently verify and certify the concurrency aspects of the result, we introduce, in Section 1.7, an efficient algorithm that checks satisfaction of the relevant safety and liveness properties in a single pass over the fuzzy multicore schedule.

### 1.2 Nested Code Graphs

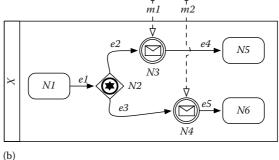

Graphs are frequently used as internal presentations for code generation and analysis purposes. We use code graphs as uniform graph syntax. One use of our code graphs is as data-flow graphs generalizing term graphs, and another use is as control-flow graphs generalizing finite-state machines and Petri nets. To express concurrent processes and parallel execution, we use the same code-graph syntax at different levels of nesting to combine data-flow aspects, control-flow aspects, and concurrency aspects in nested code graphs.

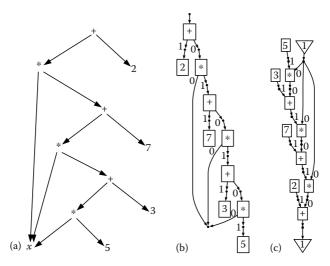

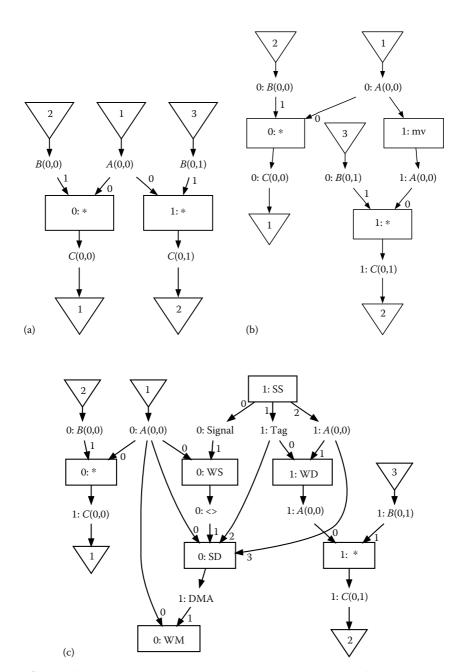

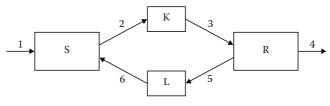

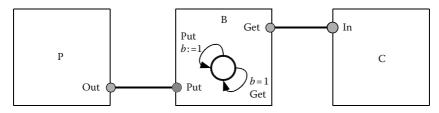

**FIGURE 1.2:** (a) Horner term graph, (b) jungle, and (c) code graph.

Term graphs, the abstract version of data-flow graphs, are usually represented by graphs whose nodes are labeled with function symbols and edges connect function calls with their arguments [37]. We use the dual approach of directed hypergraphs where nodes are labeled with type information (if applicable), function names are hyperedge labels, and each hyperedge has a sequence of input tentacles and a sequence of output tentacles (each incident with a node).

For example, Figure 1.2 shows first a conventional term graph (as presented by HOPS [27]) for calculating the polynomial  $5x^3 + 3x^2 + 7x + 2$  using Horner's rule, i.e., as x \* (x \* (x \* 5 + 3) + 7) + 2, and second a conventional jungle with nodes drawn as black discs, and edges drawn in boxes with a result tentacle from the result node to the edge and numbered\* argument tentacles from the edge to the argument nodes. Variables are represented by nodes that are not the result of any edge.

In contrast, the tentacles of our code graphs follow the direction of the data flow, and we draw the data flow downward, as shown in the right-most drawing of Figure 1.2. In our code graphs, we also explicitly flag input nodes (corresponding to jungle variables) by attaching a numbered triangle with an arrow to the node, and output (result) nodes by attaching a numbered triangle with an arrow from the node.

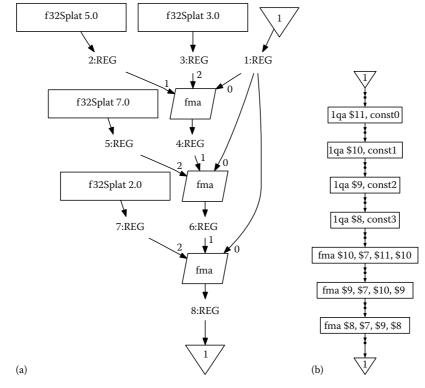

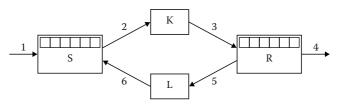

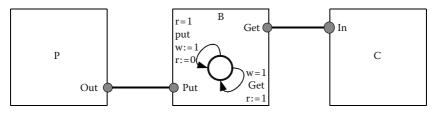

Such data-flow code graphs are the central data structure of the SPU scheduler of Coconut. The assembly-level data-flow code graph for the same polynomial is shown to the left in Figure 1.3, with edges containing in this case either the SPU SIMD opcode fma (fused floating-point multiply-add), or SIMD constants replicating (splatting) the same 32-bit floating-point number four times into 128-bit SPU registers. In this drawing, we show node numbers (normally for debugging purposes),

<sup>\*</sup> Since all these code-graph drawings have been automatically generated via dot [29], these numbers are necessary to indicate argument sequence.

**FIGURE 1.3:** (a) Horner assembly-level data-flow and (b) control-flow code graphs.

and indicate the node type "REG" standing for 128-bit SPU register values. Since the SPU has a unified register file, there are no further type distinctions at this level, although a refinement makes sense for the purpose of analyzing and verifying the data flow of individual register components, see Ref. [4].

To the right in Figure 1.3, we show the assembly instructions that the left graph is compiled to, presented as a control-flow code graph. Assembly instructions are opcodes together with argument and result registers, so the data flow can be reconstructed from this.\* For this chapter, it is central that code graphs can be used for both data-flow and control-flow graphs.

In the light of the above, a hypergraph in the sense of this paper is therefore directed, with sequences of input (argument) and output (result) tentacles at each edge:

<sup>\*</sup> The constants are transformed into data segments for the assembler, and referenced by the labels "const0", ..., "const3". This is necessary since there are no SPU instructions with immediate arguments of 32 bits.

### **DEFINITION 1.1**

A hypergraph  $H = (\mathcal{N}, \mathcal{E}, \text{src}, \text{trg}, \text{nLab}, \text{eLab})$  over a node label set NLab and an edge label set ELab consists of

- A set  $\mathcal{N}$  of nodes and a set  $\mathcal{E}$  of hyperedges (or edges)

- Two functions  $\operatorname{src}$ ,  $\operatorname{trg}: \mathcal{E} \to \mathcal{N}^*$  assigning each hyperedge the sequence of its source nodes and target nodes respectively

- Two functions nLab :  $\mathcal{N} \to \mathsf{NLab}$  and eLab :  $\mathcal{E} \to \mathsf{ELab}$  assigning labels to nodes and hyperedges

Hypergraph homomorphisms are pairs consisting of a total node mapping and a total edge mapping, preserving src, trg, nLab, and eLab, and induce a category.

If a hypergraph in some sense represents a program, it has an input/output interface:

### **DEFINITION 1.2**

A code graph G = (H, In, Out) over a node label set NLab and an edge label set ELab consists of

- Hypergraph  $H = (\mathcal{N}, \mathcal{E}, \text{src}, \text{trg}, \text{nLab}, \text{eLab})$  over NLab and ELab

- Two node sequences In, Out :  $\mathcal{N}^*$  containing the input nodes and output nodes of the code graph

A code-graph homomorphism is a hypergraph homomorphism that additionally preserves In and Out.

Typing aspects are dealt with in the usual way:

### **DEFINITION 1.3**

A hypergraph signature is a hypergraph where the labeling functions nLab and eLab are the identities on the respective label sets.

A typed hypergraph is a hypergraph together with a homomorphism into a hypergraph signature.

The resulting categories of (typed) hypergraphs have pushouts, and can therefore be used as basis for the double-pushout approach to graph transformation [11], where rules are induced by spans in the category of code graphs [4].

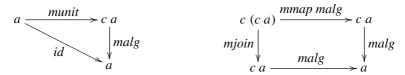

Code graphs also give rise to a gs-monoidal category with sequences of node labels as objects and code graphs as morphisms; Ref. [8] uses this to establish functorial semantics for code graphs, and Refs. [9,28] show examples where this semantics uses locally ordered categories, such that code-graph homomorphisms  $F: G_1 \to G_2$  document ordering relations  $\llbracket G_2 \rrbracket \sqsubseteq \llbracket G_1 \rrbracket$  on the semantics.

### 1.2.1 Data-Flow Graphs and Parallelism

Using code graphs as term graphs follows the jungle view of term graphs, initially put forward by Hoffmann and Plump [24,34], and equipped with functorial semantics by Corradini and Gadducci [8]. In such code graphs, nodes are labeled with types and in a certain sense represent values of the respective types; hyperedges are labeled with operations taking input values as arguments and producing results as outputs.

Data-flow semantics of hypergraphs implies the following:

- If an edge has multiple input tentacles, the computation associated with it has multiple argument positions, one for each input tentacle.

- This is the only kind of branching present in term trees. This kind of branching is also the source of potential parallelism, particularly in functional programming, since it represents a split of the computation of the outputs of this edge into potentially independent computation of its inputs.

- If a node is attached to multiple input tentacles, the value represented by this node is used by several consumers.

- This sharing marks the transition from term trees to term graphs, and is frequently only a tool for efficiency (shared effort) without semantic relevance, for example, in most implementations of functional programming. (Sharing does have semantic relevance for example in functional-logic programming [1] and in multialgebras [9,10].)

- If an edge has multiple output tentacles, the computation associated with it produces multiple results, one for each output tentacle.

- This presents a relatively unproblematic generalisation of term trees or term graphs.

- Possibility that a node is attached to multiple output tentacles was used in Ref. [28] to represent joins in data flow, i.e., different equivalent ways to produce a value.

Cycles in term graphs are frequently used to encode recursions; this normally uses a least fixed-point semantics and relies on the presence of nonstrict constructs, in particular conditionals, or, in lazy functional programming, data-type constructors.

In the central assembly-level components of Coconut, assembly op-codes (which have strict semantics) serve as edge labels, with inputs corresponding to argument registers and outputs corresponding to result registers. We use acyclic data-flow code graphs with these op-codes as edge labels to represent loop bodies of scientific computation applications, and use graph transformation and analysis to exploit instruction-level parallelism (ILP) and achieve optimal schedules [2,4].

### 1.2.2 Nonconcurrent Control-Flow Graphs

The archetypal control-flow graphs are finite-state machines; nodes are labeled with state types and represent states, and edges labeled with actions, sometimes

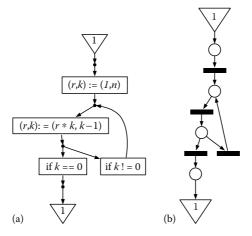

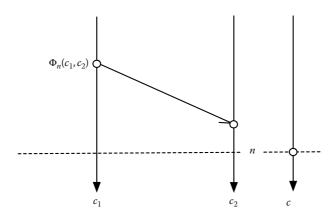

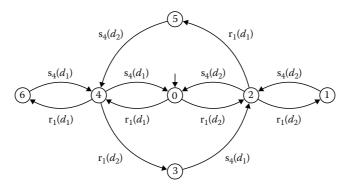

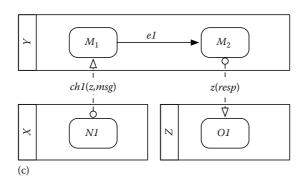

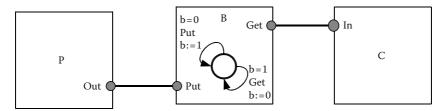

FIGURE 1.4: (a) Factorial control-flow graph and (b) underlying Petri net.

perceived as active (operations), sometimes as passive (recognition of input symbols), and sometimes as both (for example, in Mealy machines).

For conventional edges, finite-state machines serve as the standard control-flow model, and represent nonconcurrent control flow.

Cycles in control-flow graphs express iteration, and correspond to the asterate operator of Kleene algebras.

In Figure 1.4, we show the control-flow graph of an imperative implementation of the factorial function presented as a code graph. Even though from a flow-chart point of view, it may seem strange to have two separate edges for the conditional, this is in fact the way such programs are handled in relational semantics (see Refs. [17,36]), and fits well with the concurrent semantics below—indeed, abstracting all edges to transitions and considering the nodes to be places produces the place-transition Petri net (drawn to the right in Figure 1.4) representing the control flow of this program.

At the lowest (output) level in Coconut, assembly instructions (except conditional branches), i.e., op-codes together with register references, serve as control-flow edge labels, with the state before as single input, and the state after as single output.

The conversion of op-code-labeled hyperedges to instruction-labeled control-flow edges happens as part of scheduling of the data-flow graphs; since scheduling essentially means adding of control dependencies, and scheduling of a data-flow graph together with a register allocation enforces the data-flow dependencies via the stronger control-flow dependencies.

At a higher level, we represent computational kernels as sequential control-flow graphs where most of the edges are labeled with larger data-flow graphs, and implement software pipelining essentially as graph transformation on these control-flow graphs [3].

# 1.2.3 Control-Flow Graphs and Concurrency

The standard model for concurrent control flow are Petri nets, which are, in more theoretical work (e.g., [18]), formalized as directed hypergraphs, with places represented by hypergraph nodes and transitions by hyperedges (but with multisets of input and output places for each transition; Sassone introduced the concept of prenet which has sequences instead of multisets [6,35]).

Putting everything together, control-flow semantics of directed hypergraphs therefore implies the following:

• If a node is attached to multiple input tentacles, it is normally understood that control propagates along any applicable outgoing edge.

This kind of branching implements decisions by making different edges applicable depending on the circumstances. In finite-state automata recognizing regular languages, those edges whose labels match the next available input are applicable; more generally, conditions depending on the current state can be used, as for example "k = 0" in Figure 1.4. If several outgoing edges of the same node are applicable, then this kind of branching introduces nondeterminism.

If this is the only kind of branching, the resulting graphs can be used as decision trees, or as tree structures for branching-time temporal logics [15].

- If a node is attached to multiple output tentacles, the corresponding different operations pass control to the same state.

- This corresponds to moving from tree structures for branching-time temporal logics to graph structures, and similarly from infinite regular languages to finite automata; in imperative programming, this is typically induced by jumps or higher-level control structures such as loops.

- If an edge has multiple output tentacles, we understand this as forking the current thread of control into multiple threads of control.

- This corresponds to the fact that Petri net transitions with multiple outgoing edges place tokens into each successor place upon firing.

- If an edge has multiple input tentacles, we understand this as introducing synchronization of concurrent threads.

With this background, it becomes clear that, in the nonconcurrent case, conditionally branching assembly instructions should not be represented by branching hyperedges, but instead as two conventional edges of which in each state only one is applicable, as can be seen in the example shown in Figure 1.4.

# 1.2.4 Concurrent Interpretation of Data-Flow Graphs

From the theoretical literature [6,18,35] one notices that Petri net computations, which are finite acyclic versions of Petri nets equipped with a start and end interface,

give rise to essentially the same kinds of categories as term graphs, namely variants of gs-monoidal categories [8].

The description in the previous section was accordingly tuned to emphasize the compatibility between the concurrent control-flow view of a hypergraph with the data-flow view, as long as no cycles are present.

Indeed, Sassone's prenets [6], designed to reflect the "individual-token philosophy" to composition of Petri net computation, can be understood as making individual threads of control explicit.

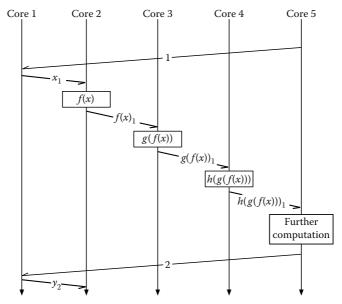

The two views combine easily into data-flow graphs with concurrency aspects, where the distribution aspects are most easily made explicit by adding host identifiers to nodes and hyperedges. For an example, see Figure 1.7.

Combining this representation of concurrency aspects of distribution with the nested hypergraph representation of sequential computational kernels, we obtain a nesting of hypergraphs with at least three levels. Implementing iteration of concurrent behavior will even require wrapping the concurrent control-flow code graph at the third level into a cyclic sequential control-flow graph, which produces a four-level nesting.

#### 1.3 Efficient Multicore Parallelism

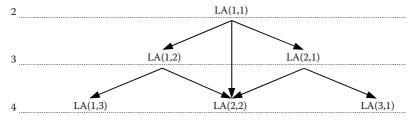

Different levels of parallelism raise different issues with respect to efficiency and correctness. It is useful to put multicore parallelism into a context categorized in order to contrast current issues with parallelism issues in the past.